# TREINADOR LÓGICO - VERSÃO 2018/2020

O treinador lógico destina-se ao desenvolvimento de experiências com circuitos digitais em Laboratório Convencional. A versão ora apresentada é um melhoramento da versão anterior.

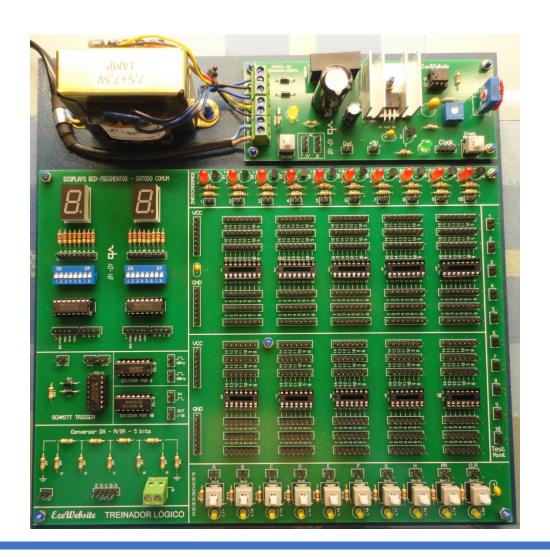

## Visão geral:

A concepção inicial desse treinador é para ensaios com circuitos integrados da família TTL, pois a fonte de tensão fornece 5 volts.

A alimentação de 5 volts também compatibiliza experiências com circuitos integrados comerciais da família CMOS, permitindo assim a interação das duas famílias em diversas experiências.

A exemplo da versão anterior, o módulo dispõe de 5 soquetes de 14 pinos e 5 soquetes de 16 pinos, permitindo assim, uma grande quantidade de experiências, desde circuitos básicos com portas lógicas primárias até circuitos mais complexos como por exemplo, contadores, registradores de deslocamento, multiplexadores etc.

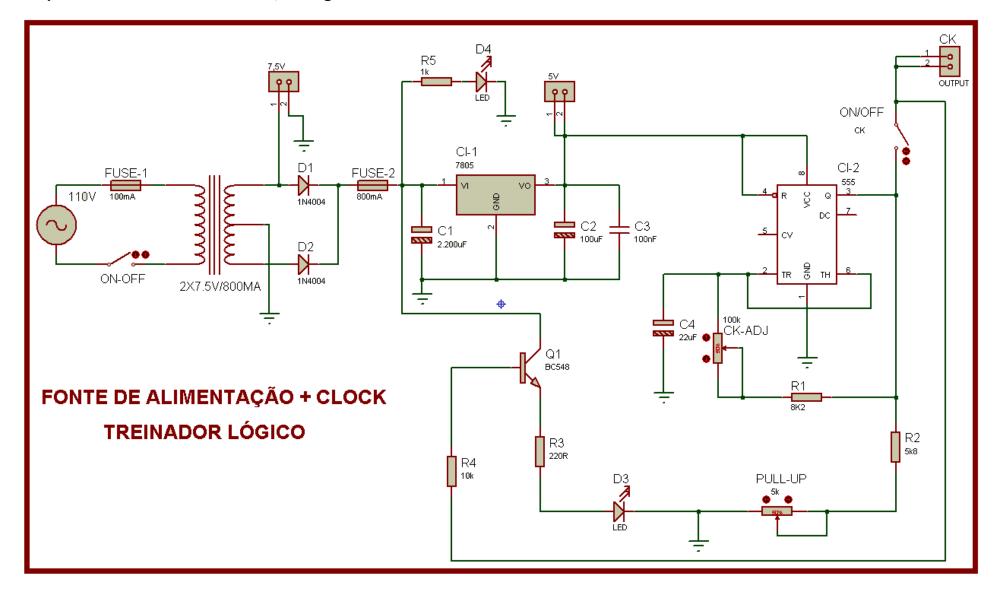

## Fonte de alimentação e gerador de clock:

Um dos diferenciais da nova versão é a fonte de alimentação, que está separada do bloco principal, assim como o gerador de clock, conforme mostra a figura a seguir:

Além da tensão de alimentação +5V regulada eletronicamente pelo CI LM7805, disponibiliza também uma saída de 7,5V AC para utilização em circuitos especiais, como por exemplo, disparador Schmitt Trigger.

O CI NE555 é responsável por gerar os pulsos de clock, cuja frequência é controlada pelo trimpot de 100k.

A frequência de clock é monitorada pelo diodo led D3, que permite assim monitorar os níveis de transição dos pulsos de clock (H-L, L-H ou nível lógico 0 ou 1).

Para não sobrecarregar o circuito é utilizado o transistor Q1 que alimenta e polariza adequadamente D3.

A chave ON/OFF serve para interromper o funcionamento do fornecimento dos pulsos de clock sem que haja a necessidade de remover fios de ligação.

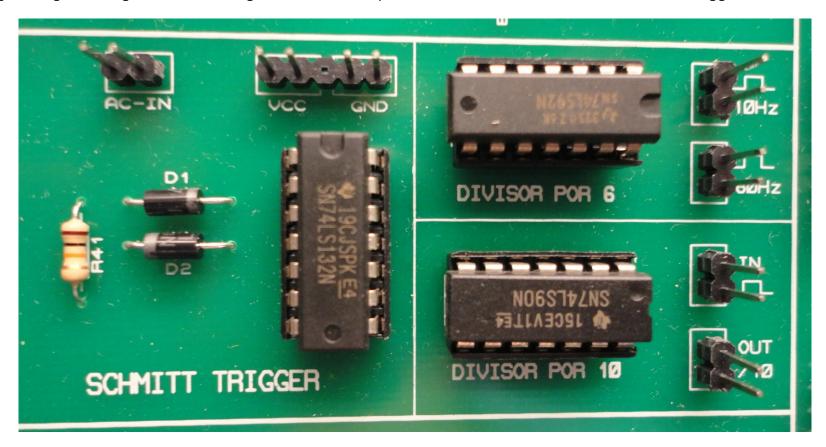

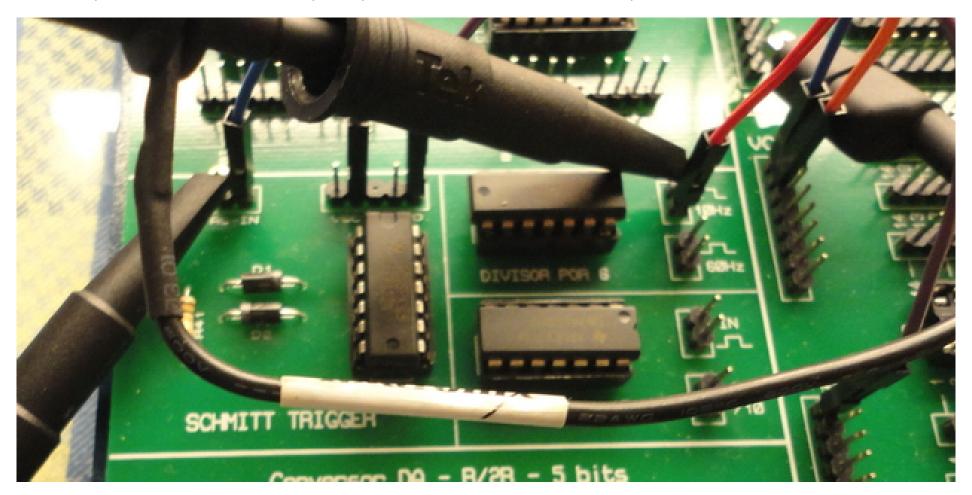

### **Disparador Schmitt Trigger:**

Veja na figura a seguir detalhes do gerador de onda quadrada através do CI 74LS132, Schmitt Trigger.

Neste caso o pulso de clock é gerado a partir de uma amostragem da tensão da rede (frequência de 60Hz), a qual é obtida do secundário do transformador utilizado na fonte de alimentação. Neste caso, a tensão disponível é de 7,5 volts AC.

Com a utilização dos CIs 74LS90 e 74LS92 é possível obter a divisão da frequência da rede por 6 e por 10.

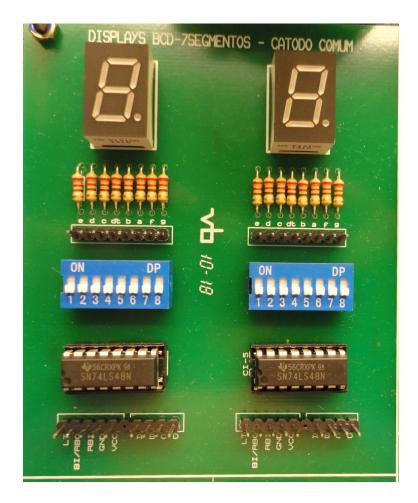

### **Displays BCD 7 segmentos:**

A novidade da nova versão é a introdução dos dois decodificadores BCD-7 segmentos (um para cada display), permitindo experimentos com os decodificadores a partir da posição ON nas chaves *dip-switch*.

Com *dip-switch* na posição OFF, os segmentos dos displays tornam-se independentes permitindo assim, outros tipos de experimentos.

## Indicadores de nível lógico de saída (1 a 10):

Em relação a versão anterior, a única modificação foi a introdução de um transistor para acionar o led, evitando assim uma possível sobrecarga (efeito *fan-out*) nas saídas dos circuitos integrados.

## Chaves de programação (A até H + PR + CLR):

Não ocorreram modificações em relação a versão anterior, lembrando apenas que os leds L1 a L10 monitoram os níveis lógicos que são aplicados.

## Sobre o resistor pull-up:

Nesta versão o resistor pull-up pode ser variado a um valor mínimo de 5k6 até 10k6, facilitando assim o controle de possíveis interferências em relação aos pulsos de clock.

O conjunto é formado pelo trimpot (pull-up de 5k) e o resistor R2 (5k6).

Vista do trimpot pull-up e o resistor R2 no módulo fonte / clock

#### Conversor DA de 5 bits:

A nova versão do Treinador Lógico incorpora um conversor DA de 5 bits montado com rede R-2R.

Os níveis lógicos para suprir as entradas EDCBA devem ser obtidos através das chaves de "programas".

## Esquema da fonte de alimentação + gerador de clock:

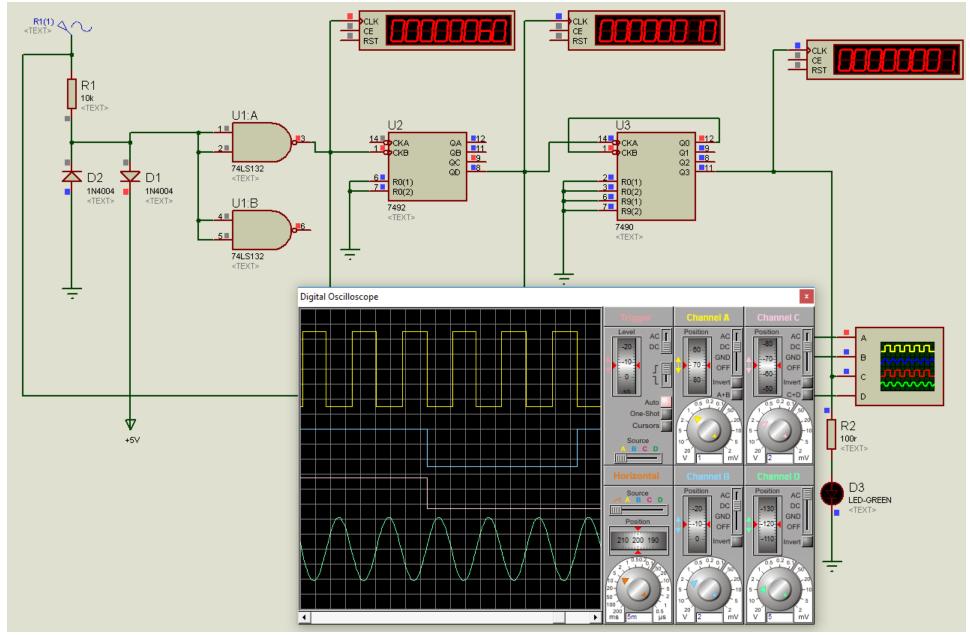

Veja a seguir o ensaio de um **disparador Schmitt Trigger** no Proteus ISIS. O primeiro CI (U2) divide por 6 e o segundo CI (U3) divide por 10. Portanto o circuito comporta-se como um divisor por 60.

Disparador Schmitt Trigger – divisor por 60 (a partir da frequência da rede 60Hz)

## **Ensaios com o disparador Schmitt Trigger:**

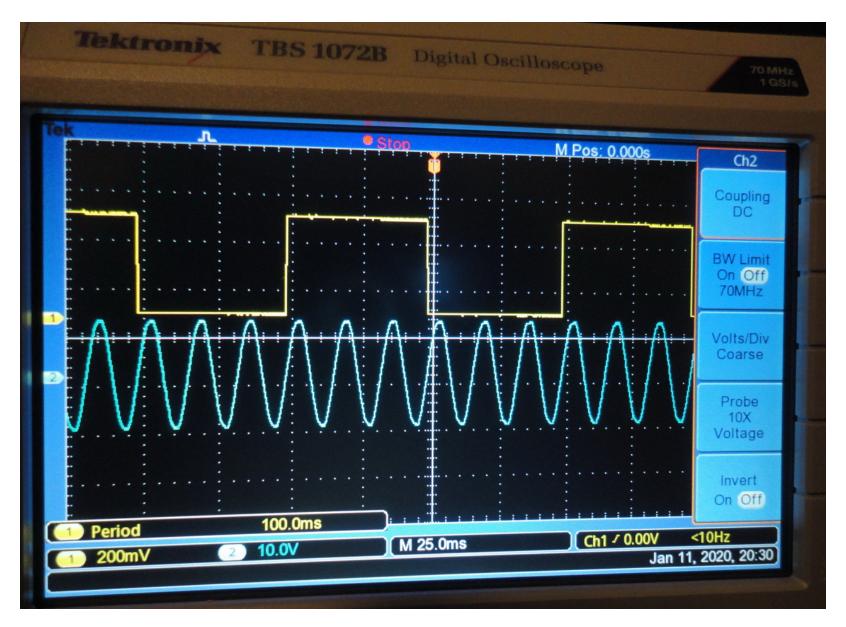

A figura a seguir mostra as formas de ondas vistas no osciloscópio a partir de uma amostragem de uma tensão AC de 7,5 volts 60Hz disponível no módulo *Fonte de Alimentação + Clock*.

A frequência de entrada é dividida por 6, portanto, na saída teremos uma frequência de 10Hz.

A divisão por 6 ocorre pela ação do CI 74LS 92.

É bom lembrar que o CI deve ser alimentado normalmente com +5V (família TTL).

Observe que o período da forma de onda na saída é de 100ms, 0 que equivale a uma frequência de 10Hz. A amplitude do sinal de amostragem aplicado na entrada é aproximadamente 23Vpp.