### Flip-Flops Sincronizados - tipo D

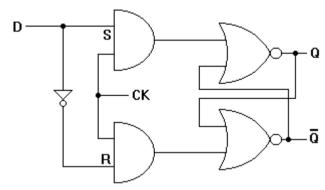

Um FF sincronizado depende diretamente de pulsos de clock para a sua liberação (enable). Veja abaixo um FF do tipo D implementado a partir de um FF RS básico.

Analisando o circuito acima, oberva-se que, se o pulso de clock for igual a zero, a entrada D estará bloqueada.

| D | СК | Qn+1 | Qn+1' | Modo de<br>operação |

|---|----|------|-------|---------------------|

| 1 | 0  | Qn   | Qn'   | bloqueado           |

| 0 | 0  | Qn   | Qn'   | bloqueado           |

| 1 | 1  | 1    | 0     | set                 |

| 0 | 1  | 0    | 1     | reset               |

Qn+1 é a condição da saída após a aplicação do pulso de clock e Qn+1' é o seu complemento.

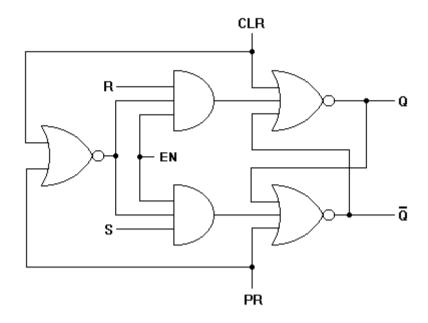

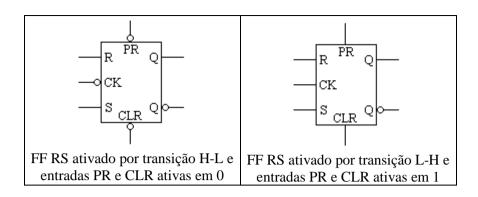

### ENTRADAS ASSÍNCRONAS PR (preset) CLR (clear)

Essas entradas são denominadas assíncronas por se sobreporem às demais entradas, em outras palavras, elas controlam o funcionamento do FF.

PR significa pré-setamento CLR significa pré-resetamento

Quando essas entradas forem ativas em 1, na condição PR=1 e CLR=0, o FF estará setado, qualquer que seja a condição das demais entradas. Caso elas sejam ativas em 0, na condição PR=0 e CLR=1 o seu modo de operação também será setado, qualquer que seja a condição das demais entradas.

A figura a seguir mostra um FF RS com entradas PR e CLR, implementado com portas NOR e AND, e com entrada de sincronização EN, isto é, o controle ou habilitação é feito em nível (0 ou 1).

OBS: FF RS controlados por nível (EN), são também conhecidos como Latch.

Tabela da verdade

| PR | CLR | EN | R | S | Qn+1 | Qn+1' | Modo de operação |

|----|-----|----|---|---|------|-------|------------------|

| 0  | 1   | X  | X | X | 0    | 1     |                  |

| 1  | 0   | X  | X | X | 1    | 0     |                  |

| 1  | 1   | X  | X | X | 0    | 0     | proibido         |

| 0  | 0   | 0  | X | X | Qn   | Qn'   |                  |

| 0  | 0   | 1  | 0 | 0 | Qn   | Qn'   |                  |

| 0  | 0   | 1  | 0 | 1 | 1    | 0     |                  |

| 0  | 0   | 1  | 1 | 0 | 0    | 1     |                  |

| 0  | 0   | 1  | 1 | 1 | 0    | 0     | proibido         |

X – significa don't care (pouco importa) – esses níveis lógicos podem ser 0 ou 1

### $1^{\circ}$ caso: PR = 0 e CLR = 0

Neste caso as entradas adicionais PR e CLR não influem no funcionamento do FF, isto é quem controla o circuito são as entradas R, S e EN.

#### $2^{\circ}$ caso: PR = 1 e CLR = 0

Neste caso o FF estará sempre setado, independentemente das entradas R, S e EN.

#### $3^{\circ}$ caso: PR = 0 e CLR = 1

Neste caso o FF estará sempre resetado, independentemente das entradas R, S e EN.

#### $4^{\circ}$ caso: PR = 1 e CLR = 1

Neste caso o FF entrará em modo proibido, situação esta que deve ser evitada.

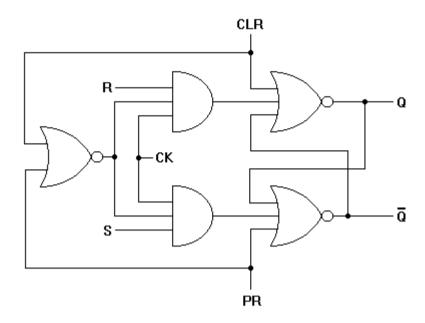

A figura a seguir mostra um FF RS com entradas PR e CLR, implementado com portas NOR e AND, e com entrada de sincronização CK, isto é, o controle ou habilitação é feito em transição L-H ou H-L.

Neste caso, a habilitação do circuito será feita na transição L-H, ou seja, na subida do pulso de clock ou borda positiva.

A subida do pulso de clock será representada por "\"

A descida do pulso de clock será representada por "\u2212"

Tabela da verdade

| PR | CLR | CK           | R | S | Qn+1 | Qn+1' | Modo de operação |

|----|-----|--------------|---|---|------|-------|------------------|

| 0  | 1   | X            | X | X | 0    | 1     |                  |

| 1  | 0   | X            | X | X | 1    | 0     |                  |

| 1  | 1   | X            | X | X | 0    | 0     | proibido         |

| 0  | 0   | $\downarrow$ | X | X | Qn   | Qn'   | veja OBS:        |

| 0  | 0   | <b>↑</b>     | 0 | 0 | Qn   | Qn'   |                  |

| 0  | 0   | <b>↑</b>     | 0 | 1 | 1    | 0     |                  |

| 0  | 0   | <b>↑</b>     | 1 | 0 | 0    | 1     |                  |

| 0  | 0   | <b>↑</b>     | 1 | 1 | 0    | 0     | proibido         |

OBS: Veja que, na descida do pulso (transição H-L) de clock as entradas R e S não influem no funcionamento do circuito, uma vez que o FF é ativo na transição L-H.

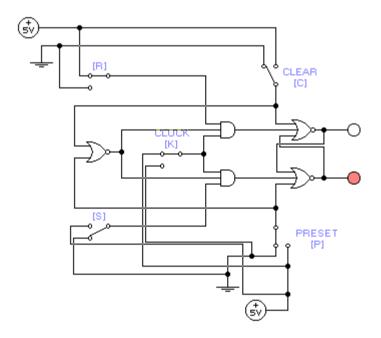

### SIMULAÇÃO NO EWB

Modo de operação RESET

$$CLR = 0$$

e  $PR = 0$

$Clock = 1$

$R = 1$  e  $S = 0$

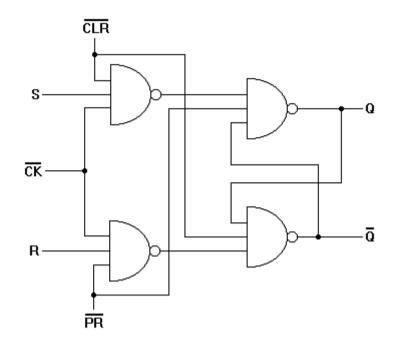

A figura a seguir mostra um FF RS com entradas PR e CLR implementado com portas NAND. É importante observar neste circuito que, as entradas PR e CLR são ativas em 0 (zero) e o pulso de clock ativa o FF na transição H-L (borda negativa).

Prof. Edgar Zuim Página 4

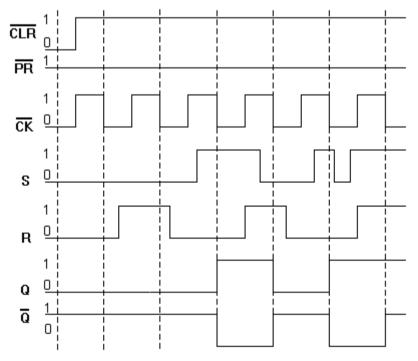

Veja a seguir a análise gráfica. Neste caso, como as entradas CLR e PR são ativas em 0, a condição inicial do FF é resetada, pois CLR = 0 e PR = 1.

## SIMULAÇÃO NO EWB

Condição de funcionamento: SET

### Tabela da verdade

| PR' | CLR' | CK' | R | S | Qn+1 | Qn+1' | Modo de operação |

|-----|------|-----|---|---|------|-------|------------------|

| 0   | 1    | X   | X | X | 1    | 0     | SET              |

| 1   | 0    | X   | X | X | 0    | 1     | RESET            |

| 0   | 0    | X   | X | X | 1    | 1     | PROIBIDO         |

| 1   | 1    | 0   | X | X | Qn   | Qn    | PROIBIDO         |

| 1   | 1    | 1   | 0 | 1 | 1    | 0     | SET              |

| 1   | 1    | 1   | 1 | 0 | 0    | 1     | RESET            |

| 1   | 1    | 1   | 0 | 0 | 0    | 1     | HOLD             |

| 1   | 1    | 1   | 1 | 1 | 1    | 1     | PROIBIDO         |

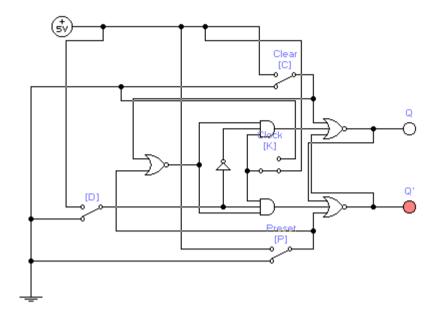

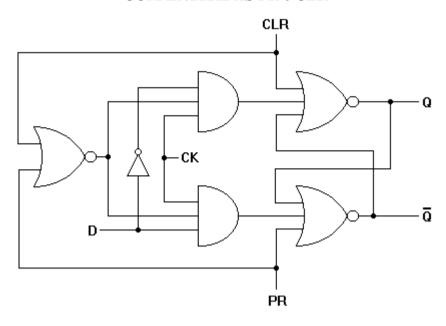

# IMPLEMENTAÇÃO DE UM FF TIPO "D" COM ENTRADAS PR e CLR

|    | ENTR | SAÍDAS        |   |      |       |

|----|------|---------------|---|------|-------|

| PR | CLR  | CK            | D | Qn+1 | Qn+1' |

| 0  | 1    | X             | X | 0    | 1     |

| 1  | 0    | X             | X | 1    | 0     |

| 1  | 1    | X             | X | IND  | IND   |

| 0  | 0    | $\rightarrow$ | X | Qn   | Qn'   |

| 0  | 0    | <b>↑</b>      | 0 | 0    | 1     |

| 0  | 0    | <b>↑</b>      | 1 | 1    | 0     |

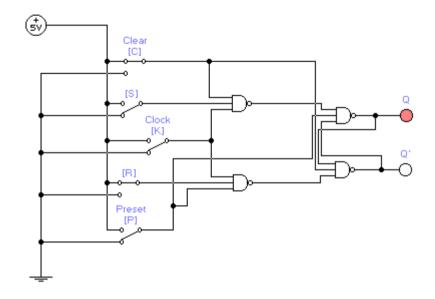

A seguir a implementação no EWB, onde as entradas PR e CLR são ativas em 1. A implementação obedece aos parâmetros da tabela acima.

Condição:

$$PR = CLR = 0$$

(liberado)

$Clock = 1$  (liberado)

$D = 0$  (reset)

## SIMULAÇÃO NO EWB